Hot Chips 31 Live Blogs: Gen-Z Chipset untuk Exascale Fabric

06:08 PM EDT – Itu bungkus, saatnya istirahat.

06:07 PM EDT – Menggunakan 16FF TSMC CoWoS

06:04 PM EDT – Cluster Kadet hingga 13 DL-385

06:03 PM EDT – Kadet adalah platform akses awal

06:03 PM EDT – Pembuatan prototipe segera hadir

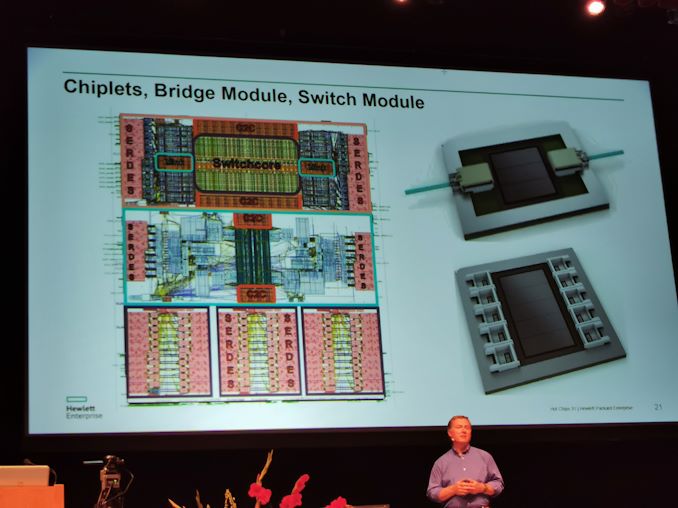

06:01 PM EDT – Ini menunjukkan tiga tipe chip

06:01 PM EDT – laboratorium

06:01 PM EDT – Tes chip sudah ada di pangkuan

06:00 PM EDT – Gen berikutnya akan menggunakan pensinyalan 400g, PCIe G5

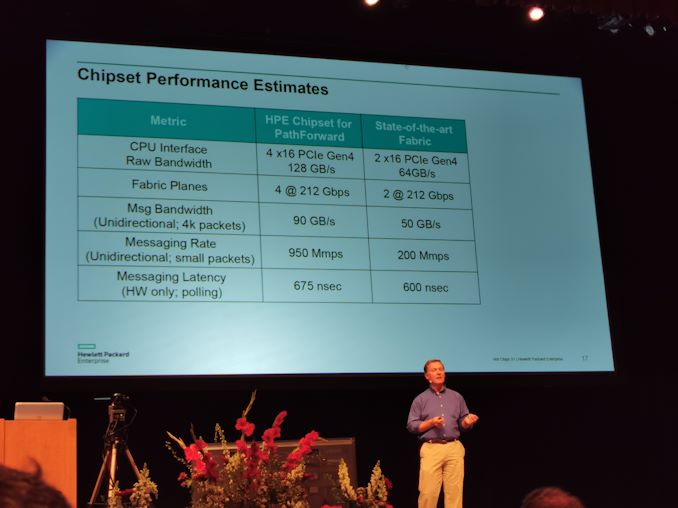

06:00 PM EDT – Pesan 5x vs kompetisi

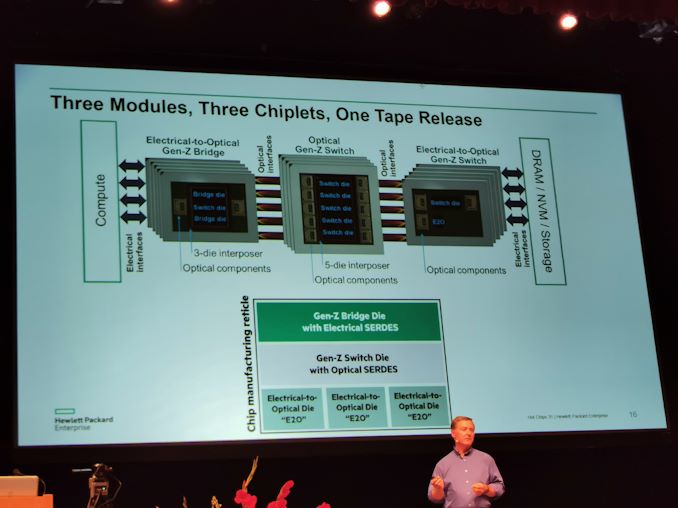

17:59 EDT – Satu penutup / satu reticle melakukan satu sakelar sakelar, satu sakelar jembatan, dan tiga modul e20

17:59 EDT – Semua dibuat dengan satu set topeng

17:58 EDT – Menggunakan bridge die dan switch die

17:58 EDT – Juga memiliki modul listrik ke optik

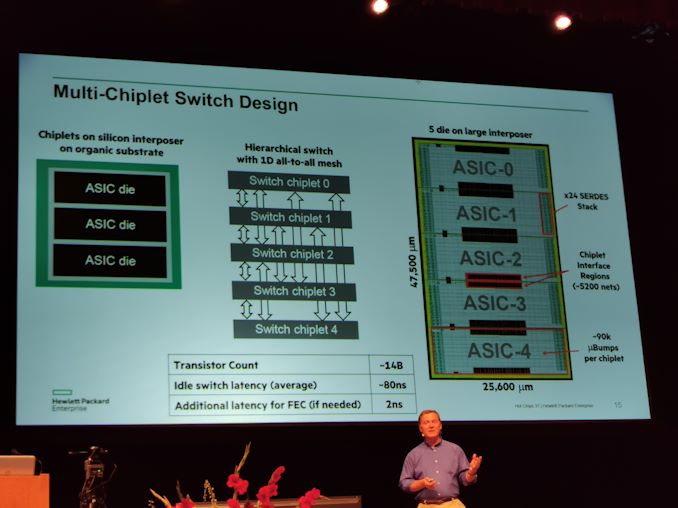

17:58 EDT – latensi sakelar siaga 80ns

17:57 EDT – 1D semua untuk semua mesh

17:57 EDT – 25.6mm x 47.5mm dengan 5 chip

17:57 EDT – Transistor 14B

17:57 EDT – Kemasan 2.5D

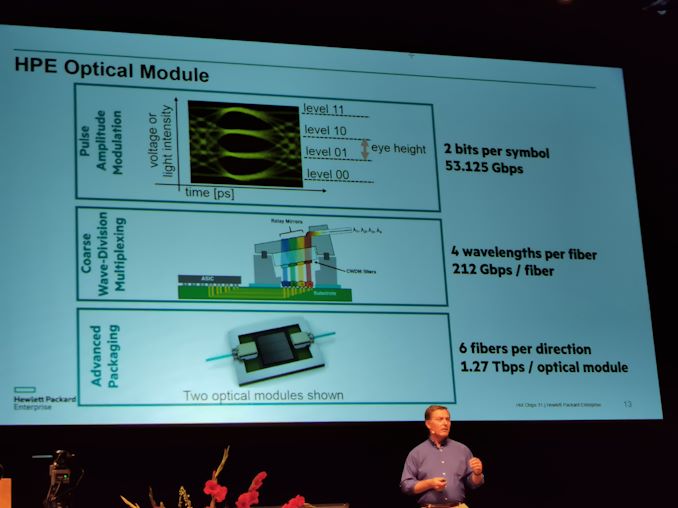

17:56 EDT – 6 serat per diksi = 1,27 Tbps per modul optik

17:56 EDT – 212 Gbps per serat dengan 4 serat

17:56 EDT – 2 bit per simbol dengan PAM4

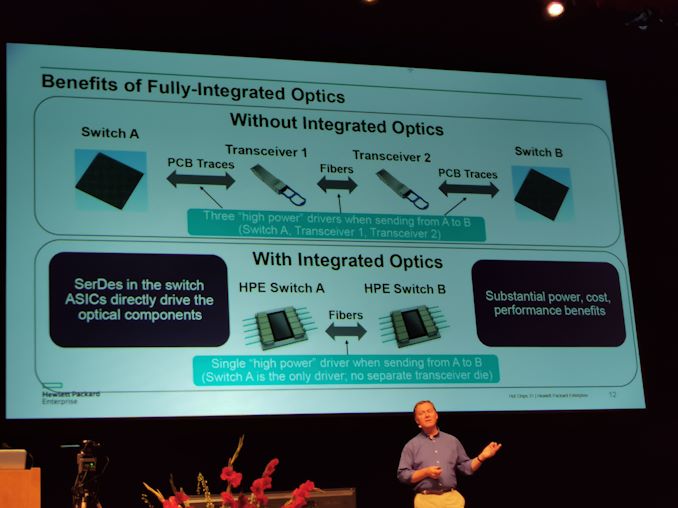

17.55 EDT – Optik terintegrasi ke dalam chipset menghindari perlunya aktivasi SerDes berlebih

17.55 EDT – Optik menyederhanakannya, dan menghemat daya

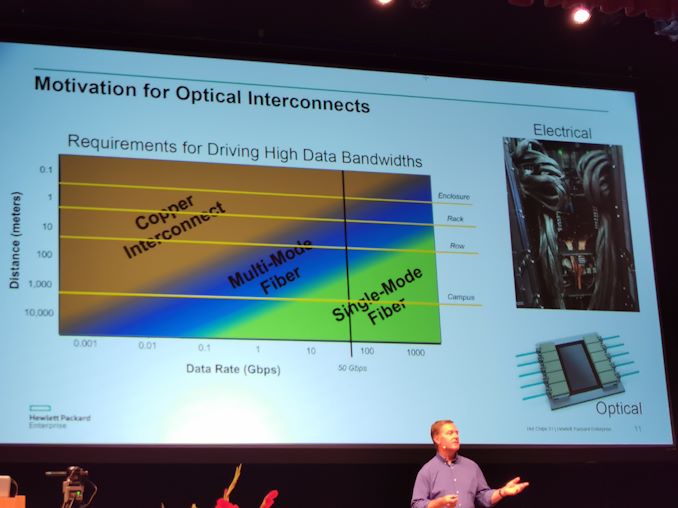

17:53 EDT – Dapat bersaing dengan tembaga di rak

17:52 EDT – Motivasi untuk interkoneksi optik

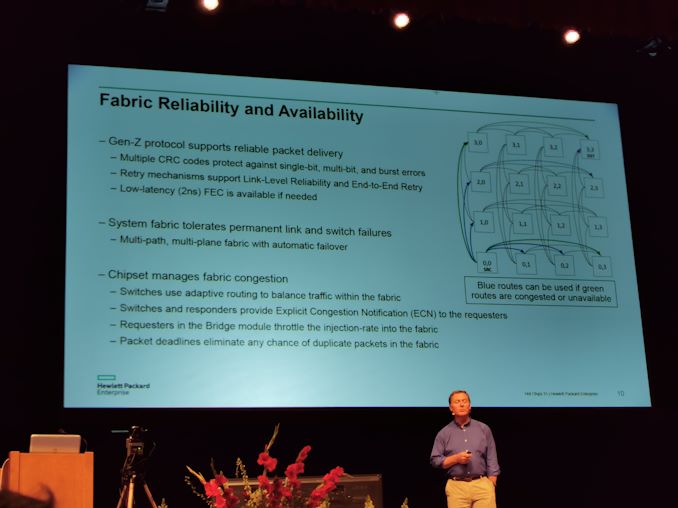

17:52 EDT – Batas waktu paket menghilangkan kemungkinan ada paket duplikat di fabric

5:51 PM EDT – Dukungan pemberitahuan kemacetan eksplisit untuk pemohon

5:51 PM EDT – Chipset mengatur kemacetan kain

05:50 EDT – FEC 2ns latensi rendah tersedia jika diperlukan

05:50 EDT – 3 tingkat CRC berbeda, 2 tingkat coba lagi

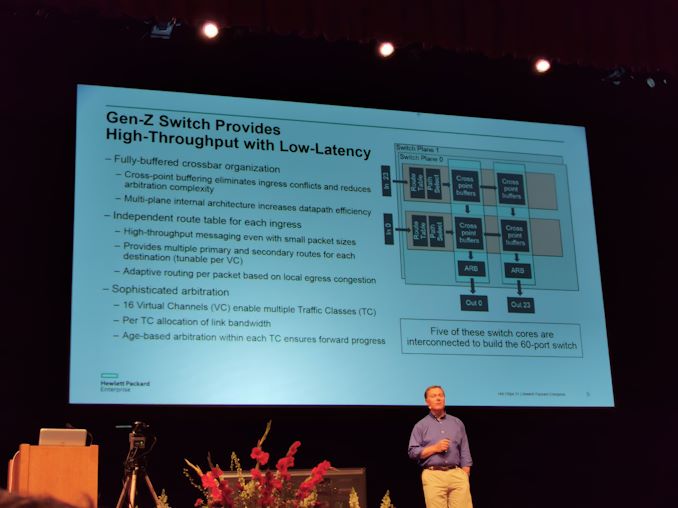

05:49 EDT – Lima sakelar ini saling terhubung untuk membangun sakelar 60-port

05:48 PM EDT – arbitrase berbasis usia

05:48 PM EDT – 16 saluran virtual

05:48 PM EDT – Organisasi palang sepenuhnya buffered

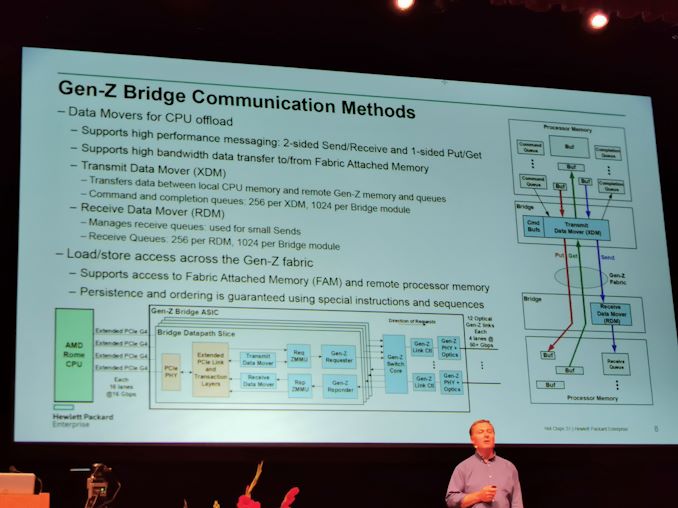

05:48 PM EDT – Dapat melakukannya untuk semua memori kain yang terpasang

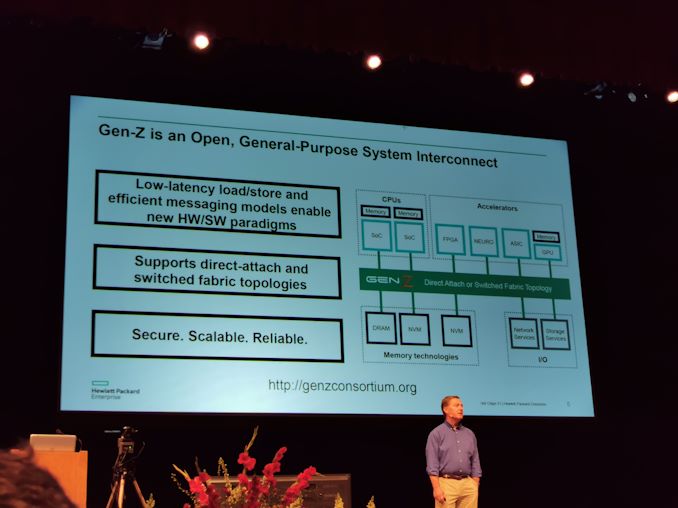

05:47 PM EDT – Mendukung akses load-store langsung

1946 EDT – Menyediakan 12 tautan Gen-Z optik

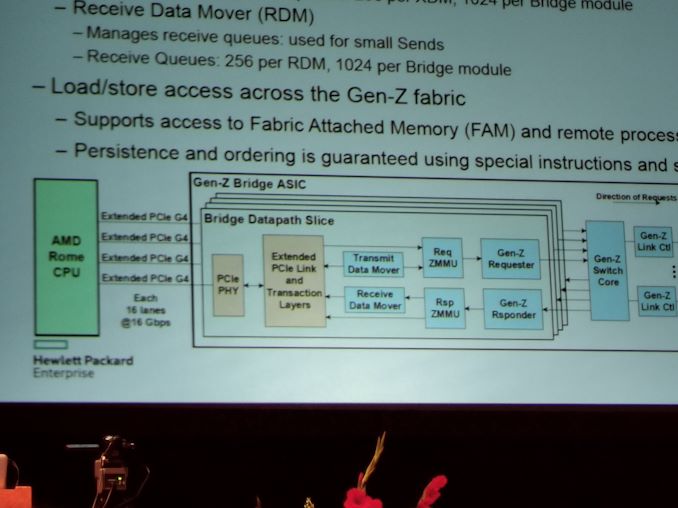

1946 EDT – Jembatan Gen-Z terhubung ke empat tautan x16 PCIe 4.0

1946 EDT – Dibangun dengan Roma karena memiliki cukup PCIe

19:45 EDT – Jembatan diperlukan karena tidak ada CPU asli Gen-Z hari ini

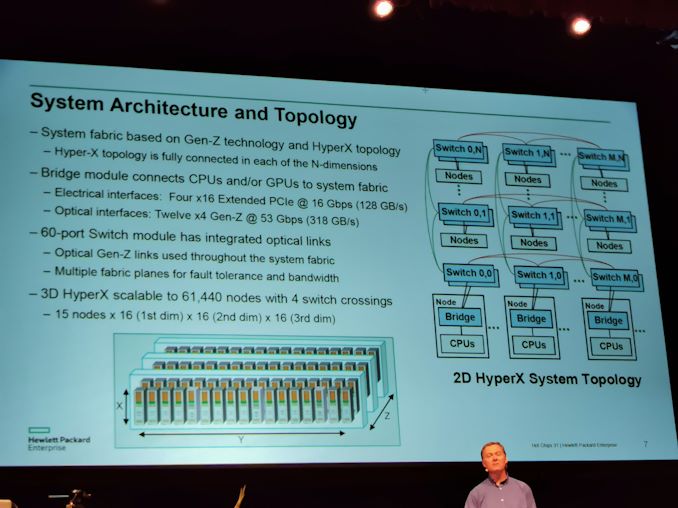

19.44 EDT – Modul switch 60-port memiliki tautan Gen-Z optik terintegrasi

19.44 EDT – 3D HyperX dapat diskalakan hingga 61440 node dengan 4 persimpangan swich

19.44 EDT – Mengembangkan topologi untuk membuat struktur sistem berdasarkan topologi Gen-Z dan HyperX

05:43 PM EDT – Mendukung pemasangan langsung dan penggantian kain

05:43 PM EDT – Mendukung interkoneksi berbasis cluster

05:43 PM EDT – Gen-Z adalah semantik memori

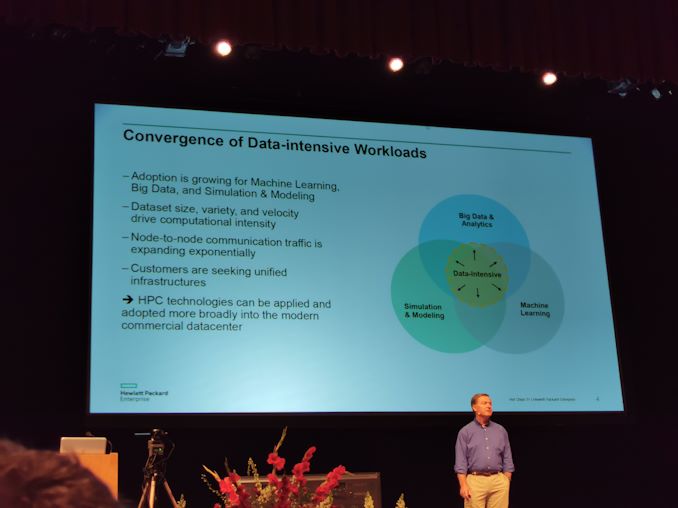

05:42 PM EDT – Pelanggan melakukan beban kerja ini, dan membutuhkan infrastruktur untuk melakukannya

05:42 PM EDT – Ukuran dataset menciptakan kompleksitas dan persyaratan komputasi

05:41 PM EDT – Analisis dan pemodelan data besar adalah apa yang pelanggan jalankan

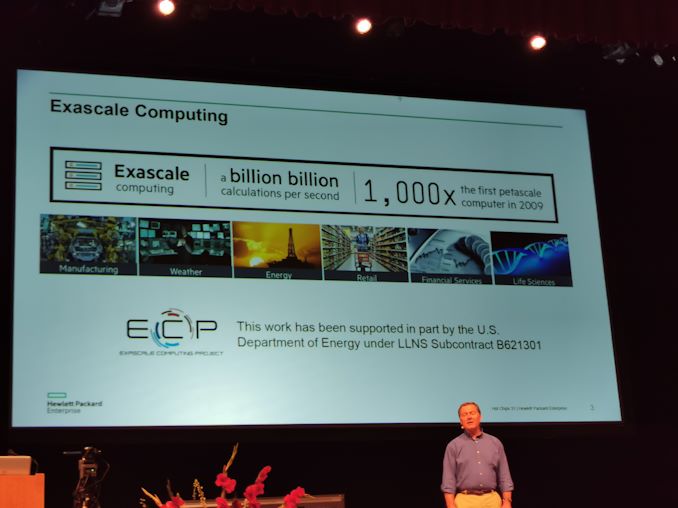

05:41 PM EDT – Didanai sebagian oleh DoE

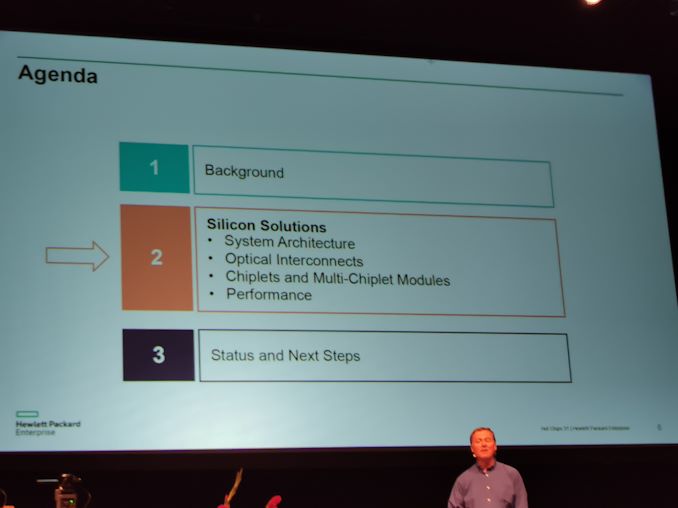

05:40 PM EDT – Salah satu interkoneksi utama yang saling bersaing di masa depan adalah Gen-Z, dan Hewlett Packard Enterprise memiliki chipset Gen-Z untuk ditampilkan di Hot Chips hari ini.