Hot Chips 31 Live Blogs: Inferensi Chip Intel 10nm Spring Hill NNP-I

03.39 EDT -.

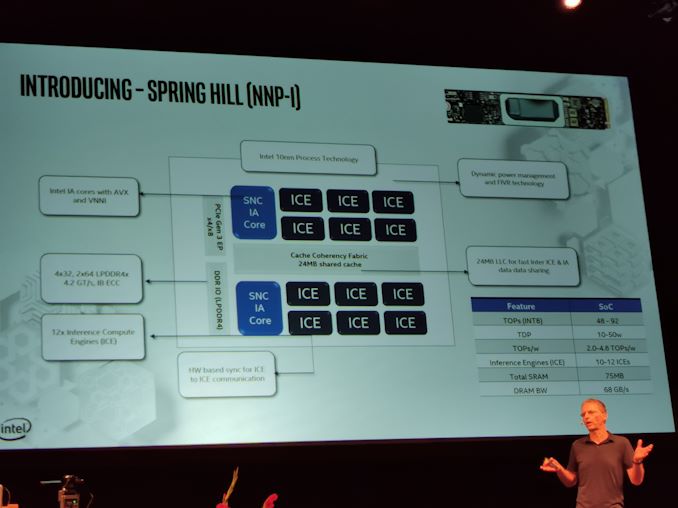

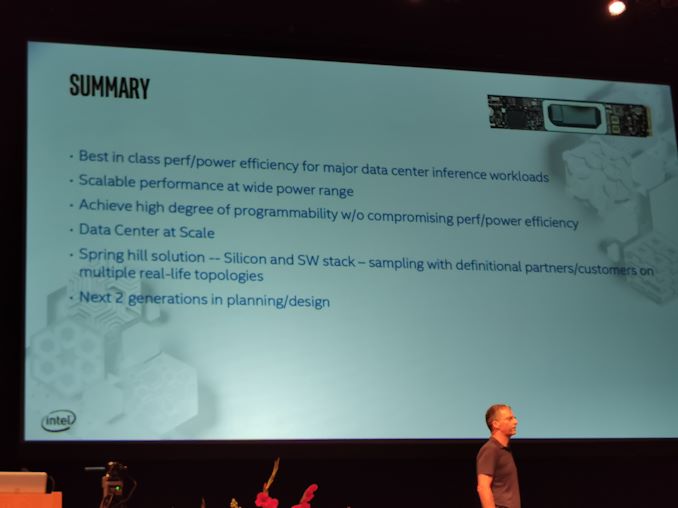

03:05 EDT: Salah satu produk 10nm masa depan Intel adalah mesin inferensi Spring Hill NNP-I 1000. Hari ini, perusahaan mengangkat tutup pada bagian arsitektur di belakang chip.

03:05 EDT – Ini adalah chip 10nm!

03:05 EDT – Informasi lebih lanjut segera hadir. Mereka memberi tahu saya tentang ini

03:06 EDT – Saya masih belum punya waktu untuk menulisnya. Tapi ini blog langsung.

03:07 PM EDT – Pentingnya pembelajaran mesin dan kesimpulan

03:07 PM EDT – Arsitektur chip itu penting

03:09 PM EDT – Chip Intel internal murni

03:09 PM EDT – Hadir dalam faktor bentuk M2 dan faktor bentuk khusus

03:10 PM Modul EDT – M.2 ditampilkan dilengkapi DRAM 16 GB

03:10 PM EDT – 5 menit dan masih pada slide pengantar

03:11 PM EDT – Hingga 4,8 TOP / W

03:11 PM EDT: silikon yang sama dapat mencapai 10W hingga 50W

03:11 PM EDT – Ini adalah chip DC

03:11 PM EDT – Berisi core Intel Sunny Cove

03:11 PM EDT: Stack SW yang mendukung semua kerangka DL utama

03:11 PM EDT: Memiliki Sunny Cove berarti AVX-512 di dalamnya

03:14 EDT – Fitur RAS untuk DC

15:15 EDT – Masih di slide ini

03:16 PM EDT – 2 Sunny Cove Cores, 12 Central Inference, 24 MB cache bersama

03:16 PM EDT – ‘ES’. Tapi bukan Danau ICE

03:16 PM EDT – Ini pada dasarnya adalah chip grafis inti Ice Lake 8 dan 6 inti dihapus, dan ICE pindah

03:17 PM EDT: dukungan DRAM yang sama dengan Ice Lake

15:18 EDT: Setiap inti Sunny Cove dapat mengendalikan salah satu dari 12 Inti Es ini

15:18 EDT: Koneksi PCIe 3.0 x4 / x8 ke host CPU

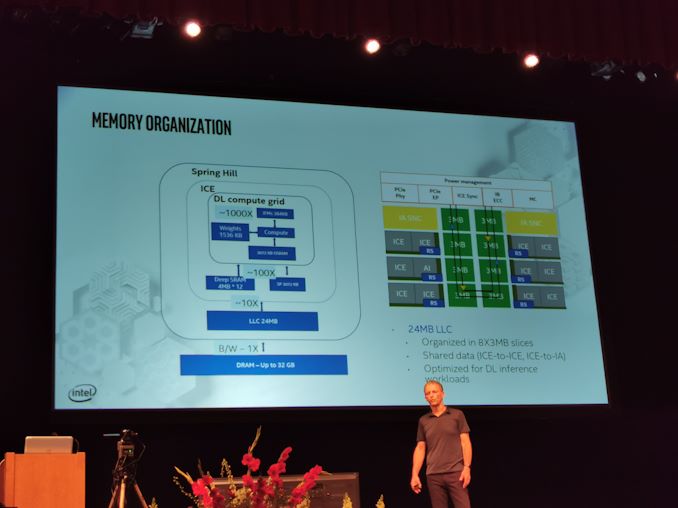

15:18 EDT – Total SRAM 75MB, BW DRAM 68 GB / s

15:19 EDT: lebih dari 10 simpul proses

15:19 EDT: dirancang untuk masalah dengan daya terbatas

15:19 EDT: Manajemen daya sama dengan Ice Like

15:19 EDT – Danau

03.20 EDT – Tetapkan beban kerja ke anggaran energi yang ditetapkan

03.20 EDT – Perangkat PCIe Standar

03:21 EDT: dalam mode 50W, jelas bukan drive M.2

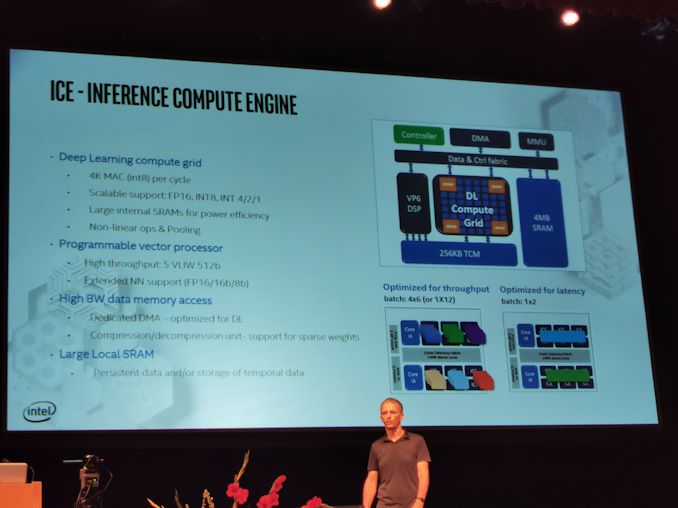

15:22 EDT – Setiap ICE dapat melakukan 4K MAC / cycle

03:23 EDT – Mendukung FP16 / INT8 / 4 / / 2 / / 1

03:23 EDT – DMA yang secara khusus dioptimalkan untuk DL

03:23 EDT – Unit kompresi / dekompresi untuk kelangkaan

03:24 EDT – 4MB SRAM melalui ICE dengan 256KB TCM antara Compute Grid / Vector DSP

3:24 EDT – Tensilica V6 DSP oleh ICE

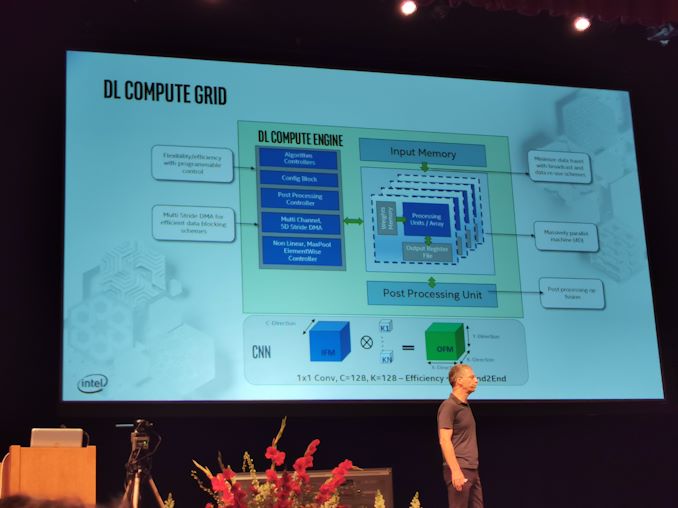

15:25 EDT – Mesin hitung DL terlihat seperti kotak 4D

15:25 EDT – 5D Stride DMA

15:25 EDT – Pemrosesan Pasca Operasi

03:26 EDT – Minimalkan transfer data

03:26 EDT – ElementWise Maxpool pengontrol nonlinier

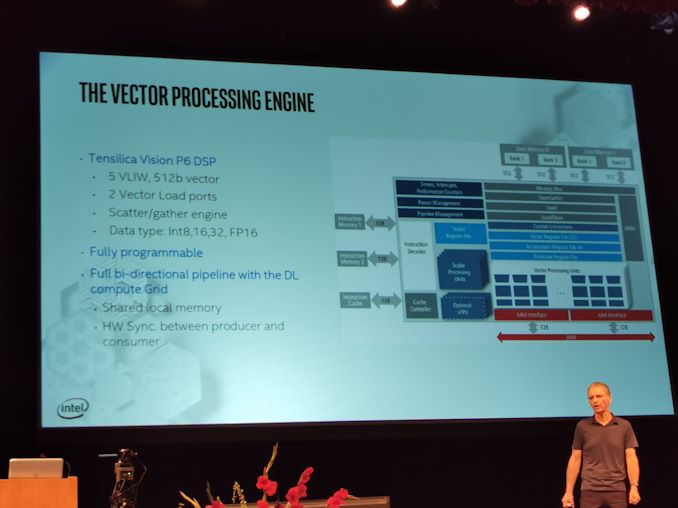

03:28 PM EDT – DSP memiliki 2 port pengisian vektor, mendukung motor pencar / kolektor asli

03:28 PM EDT – Diprogram sepenuhnya

03:28 PM EDT – pipa dua arah dengan komputasi grid DL dengan memori lokal bersama dan sinkronisasi perangkat keras

03:28 PM EDT – 4 tingkat memori

03:29 EDT – Ini seperti inti es 8 dengan inti yang terkoyak dengan 2 ICE yang dimasukkan

3:29 EDT – DRAM hingga 32GB

03:29 EDT – Tidak ada dukungan BF16

03:30 EDT – ResNet-50, 3.600 inferensi per detik pada 10W

03:31 PM EDT – Jalan tengah 2 hingga 12 memberikan kecepatan 585x

03.39 EDT – Itu bungkus. Waktu makan siang Selanjutnya adalah TSMC Keynote pukul 13:45 PT.