Hot Chips 31 Live Blogs: Intel Lakefield dan Foveros

07:14 EDT – Salah satu perkembangan menarik dalam teknologi pengemasan dalam memori baru-baru ini adalah penumpukan 3D teknologi Foveros baru Intel. Chip pertama yang menggunakan teknologi pengemasan ini disebut Foveros, dan hari ini kami berbicara tentang chip tersebut.

19:15 EDT – Akan mulai dalam satu menit atau lebih

07:17 PM EDT – Kami tahu banyak tentang Lakefield dan Foveros: stacked logic dan IO die, dengan POP DRAM. Hybrid x86 dengan 1x Sunny Cove dan 4x Tremont

07:17 PM EDT – Ini adalah sesi pengemasan pada Hot Chips, jadi kita bisa belajar lebih banyak tentang Foveros

07:17 PM EDT – Lakefield untuk ponsel cerdas dan laptop

19:18 EDT – Komputasi terbaik di kelas dalam faktor bentuk yang lebih kecil

19:18 EDT – Permintaan pelanggan

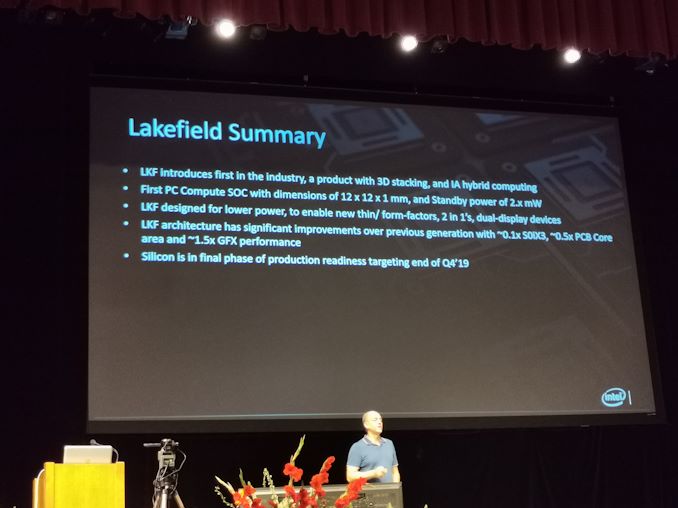

19:18 EDT – Banyak persyaratan, termasuk daya siaga 10nm dan 2mW

19:19 EDT – Juga harus kecil

19:19 EDT – dan kinerja tinggi

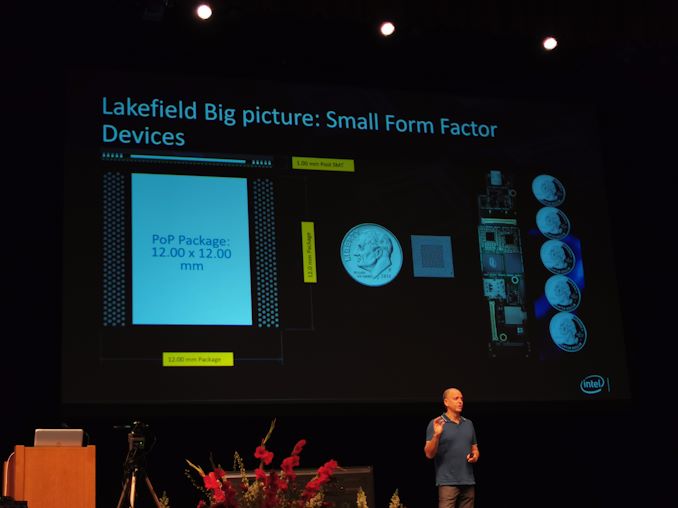

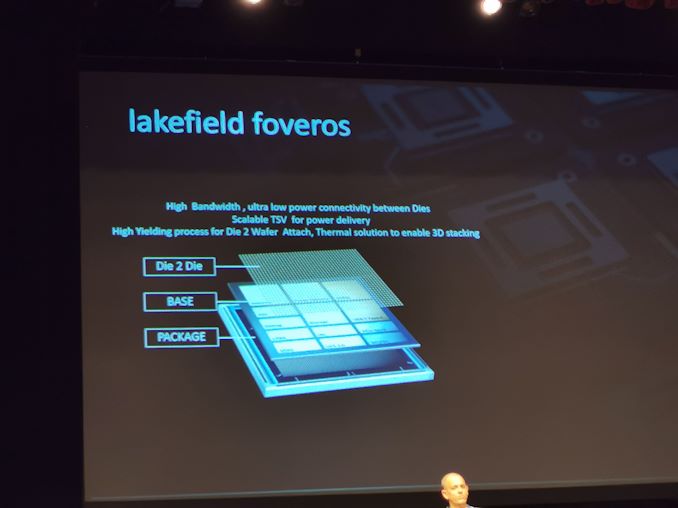

19.20 EDT – Menghitung Die, base die, dan memori 4GB (4 Gb?) Di atas

19.20 EDT – Tinggi 1mm z dengan post-SMT

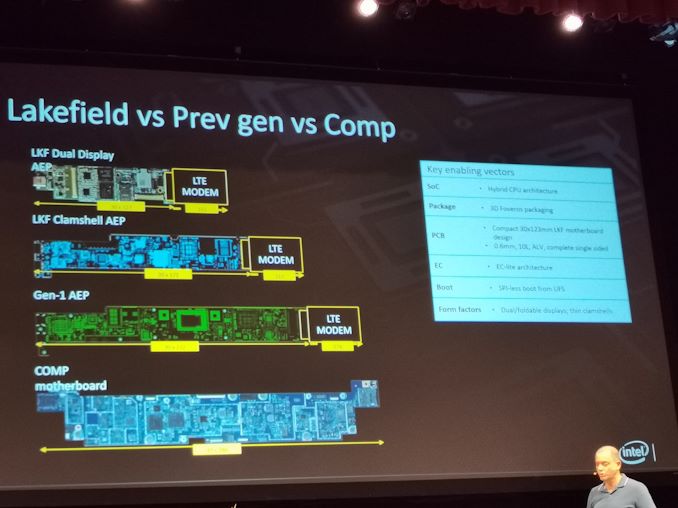

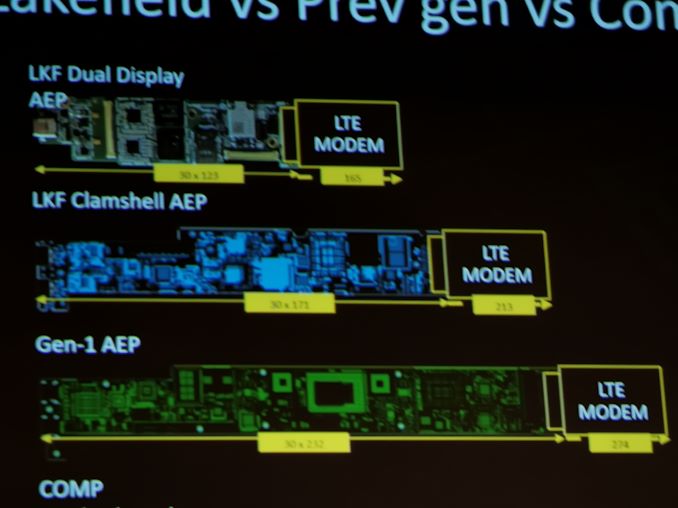

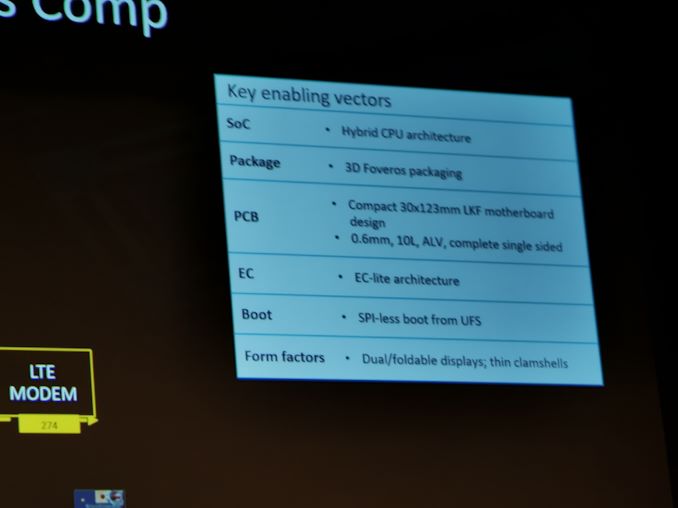

19:21 EDT – 30×123 PCB untuk penghitungan penuh pada PCB

19:21 EDT – Solusi terlengkap dari Intel

19:22 EDT – Pesaing PCB adalah 43×286 mm

19:22 EDT – Pesaing memiliki modem LTE onboard, Intel tidak

19:22 EDT – LKF Clamshell AEP adalah apa yang akan kita lihat di notebook

19:22 EDT – PCB adalah 10 lapisan

07:23 EDT – Boot SPI-less dari UFS

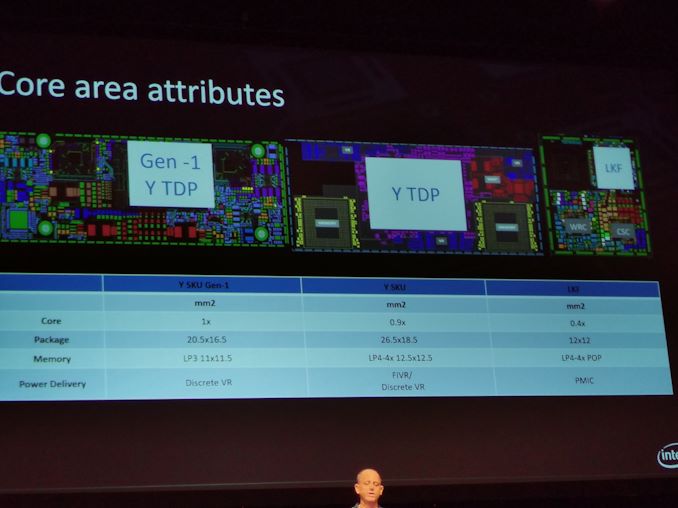

07:23 EDT – Membandingkan CPU generasi terakhir Y vs LKF

19:24 EDT – Amber vs Ice-Y vs Lakefield

19:24 EDT – Pengiriman Daya adalah PMIC

19:24 EDT – Dua PMIC di LKF, satu untuk Compute die, satu untuk IO die

19.25 EDT – Hitung dalam 10+

19.25 EDT – (Sekali Lagi, komputer dengan peragaan tidak memiliki font Intel)

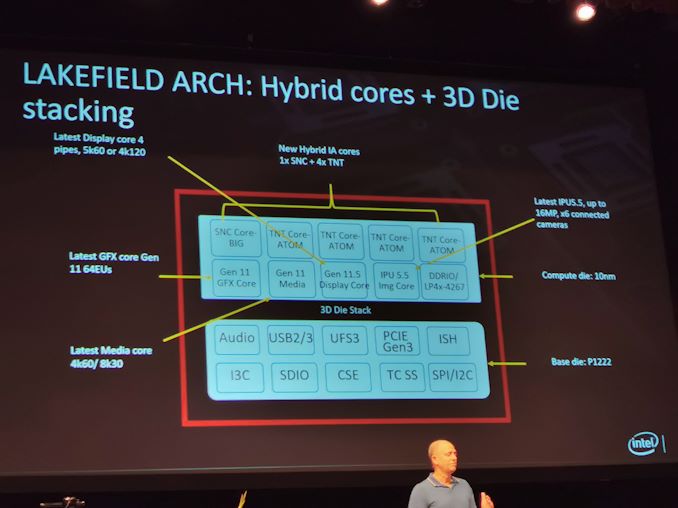

19.25 EDT – 1x Sunny Cove + 4x Tremont

19:26 EDT – Dapat mendukung hingga 6 kamera

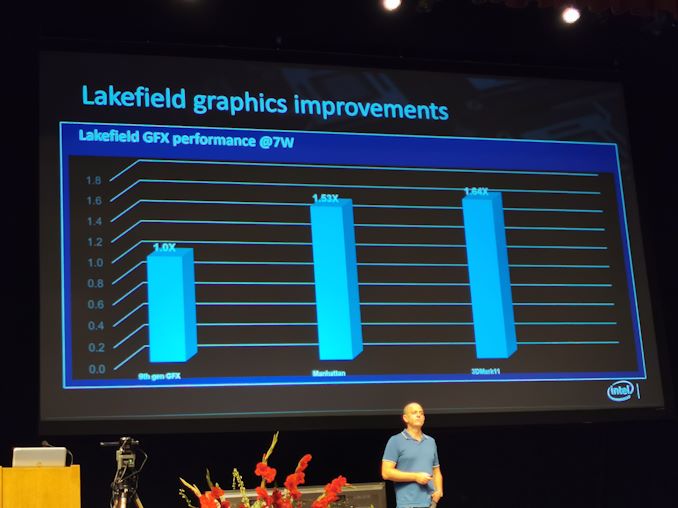

19:26 EDT – Gen 11 grafis, 64 EU

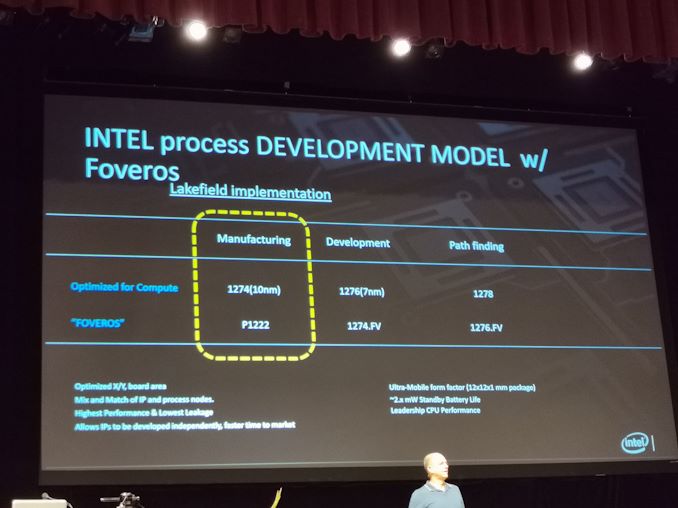

19:26 EDT – Base Die adalah P1222

19:28 EDT – P1222 adalah 10nm

19:28 EDT – 7nm dalam pengembangan

19:28 EDT – Maaf, P1222 bukan 10nm. ini 14nm

19:28 EDT – Multi-die berperilaku seperti mati monolitik

19:29 EDT – Memungkinkan IP dikembangkan secara mandiri, waktu lebih cepat ke pasar

19:29 EDT – Berencana untuk membuat lebih banyak SoC ditumpuk

19.30 EDT – (Slide baru ini bahkan tidak memiliki modal L untuk Lakefield)

07:31 PM EDT – DRAM 4 GB, atau solusi LPDDR4X 8 GB

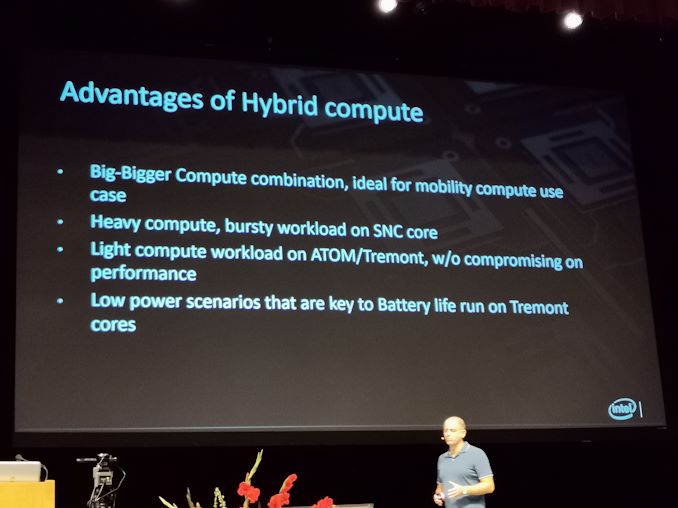

07:31 PM EDT – Sekarang Hitung hibrida

19:32 EDT – Skenario daya rendah kunci untuk masa pakai baterai dijalankan pada Tremont

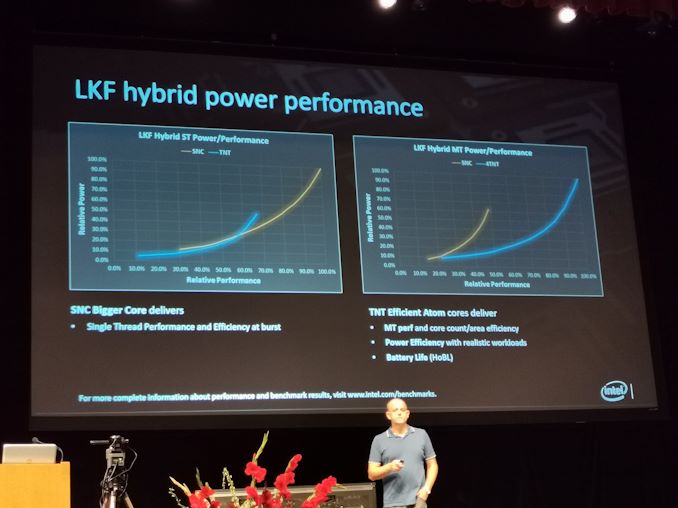

19:32 EDT – Ada kurva power / perf untuk Sunny vs Tremont

07:33 PM EDT – ST perf pada SNC, daya rendah di Tremont

19:34 EDT – Slide ini juga mengatakan lebih baik menjalankan MT di Tremont

19:34 EDT – So Sunny hanya digunakan untuk beban kerja latensi tipe respons

19:34 EDT – (Apa artinya ini untuk beberapa beban kerja yang berjalan pada saat yang sama)

19:35 EDT – (Orang yang membuat slide ini benar-benar tidak suka huruf kapital dalam judul)

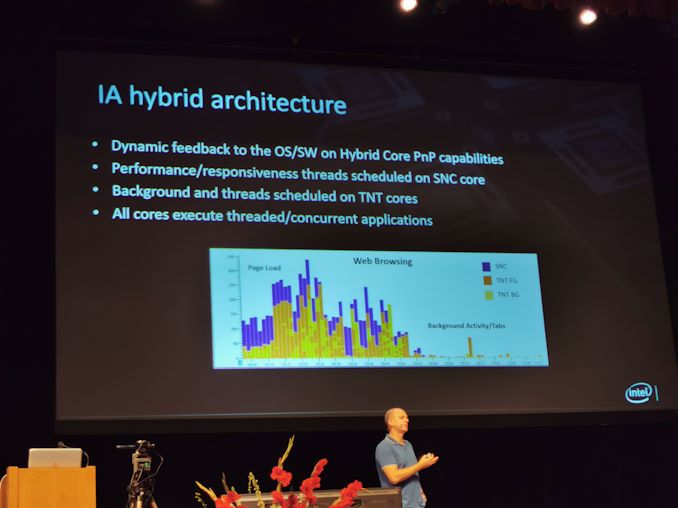

19:35 EDT – Arsitektur Hibrid menunjukkan TNT sebagai basis, dengan SNC dijalankan di bagian tertentu

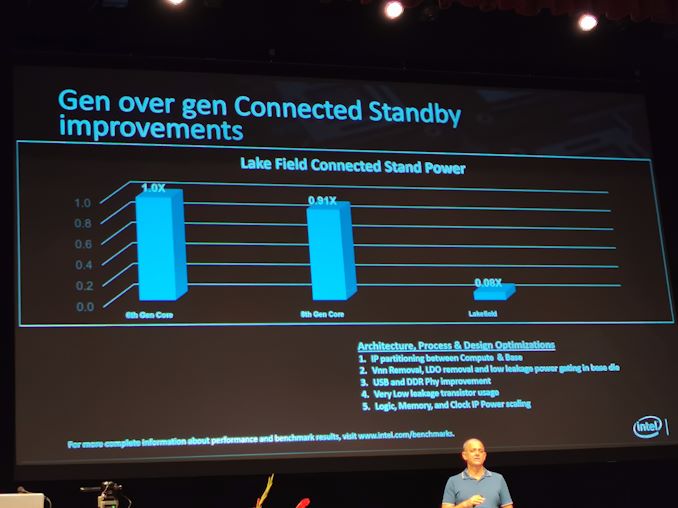

07:36 EDT – Daya siaga lebih dari 0,08x di atas Skylake

07:37 EDT – Penghapusan Vnn, penghapusan LDO, daya kebocoran rendah

07:37 EDT – Tidak perlu menggunakan transistor perf tinggi di sini. Dapat memanfaatkan transistor kebocoran rendah

07:38 PM EDT – PC Compute SoC Pertama

07:38 PM EDT – Fase pertama produksi, menargetkan kesiapan pada Q4 2019

07:39 EDT – T&J?

07:39 EDT – T: Apakah 10 atau 10+? A: 10+

19:40 EDT – T: Interkoneksi antara IO die dan Compute die? A: Potong serialisasi dan buat vertikal

19:40 EDT – T: Ikatan tatap muka dua mati? A: Ya

07:41 EDT – T: Bagaimana kekuatan dan IO dikirim melalui koneksi itu? A: Kombinasi TSV

07:42 EDT – T: nada microbumps? A: Pitch 50 mikron, tinggi 20 mikron

07:42 EDT – T: Dapatkah semua fungsi mati secara terpisah atau bersama? A: Dapat berfungsi secara independen seperti PC normal

07:44 EDT – T: Penalti karena dijauhkan dari vias? A: Aturan desain sangat memaafkan – ada banyak kelas sirkuit yang dapat bersebelahan dengan vias yang dapat membuatnya bekerja. Anda tidak akan menggunakan kecepatan tinggi, tetapi pada produk ini sangat mudah dikirim.

07:45 EDT – T: Dapatkah Anda meningkatkan skala ke daya yang lebih tinggi, dengan seperti GPU diskrit di atas? Bagaimana hal itu mempengaruhi aturan mati? A: Kami tidak melihat batas daya, kami pikir itu akan memindai seluruh rentang spektrum. Atau skala mati untuk mati. Ini masalah teknologi dan ramping, kemudian pengiriman daya. Ini semua tentang mengatasi kerugian. Kami tidak melihat batasan besar dari membatasi penumpukan 3D.

07:46 EDT – T: Bisakah Anda menumpuk lebih banyak dadu? Termal? A: Foveros adalah CoWoP dengan Silicon on Silicon, seharusnya tidak ada batasan. Manfaat melampirkan banyak chiplet. Batas praktis lain dalam partisi arsitektur. Tujuan kami adalah mengendarainya ke banyak chiplet.

07:46 EDT – Itu bungkus. Sekarang Xeon Jintide!