Xilinx Mengumumkan FPGA Terbesar Dunia: Virtex Ultrascale + VU19P dengan Sel 9m

Kami tidak sering membahas pasar FPGA di sini di AnandTech, tetapi dalam beberapa tahun terakhir kami telah melihat serangkaian fitur yang sedang dikembangkan oleh FPGA dengan laju yang luar biasa. Xilinx telah menjadi yang terdepan dalam inovasi tersebut, dengan produk-produk seperti Versal pada 7nm dan keluarga Alveo-nya. Salah satu bagian penting dari bisnis Xilinx adalah emulasi dan simulasi, yang membutuhkan FPGA besar agar sesuai dengan desain besar – dan perusahaan baru-baru ini mengangkat tutup pada kreasi terbarunya, Virtex Ultrascale + VU19P. FPGA baru ini, ketika datang ke pasar, akan menyandang gelar FPGA Terbesar Dunia.

FPGA besar adalah Bisnis Besar

FPGA, atau Field Programmable Gate Array, adalah sedikit perangkat keras yang membantu perancang sirkuit mengerjakan pekerjaan mereka. FPGA sangat dapat diprogram sehingga pengguna dapat merancang sirkuit terintegrasi pada FPGA sebelum desain masuk ke pasar, dan insinyur dapat melihat apakah desain berfungsi, dan mendapatkan perkiraan kasar tentang kinerja dan akurasi. Misalnya, pada FPGA terbesar saat ini, Virtex Ultrascale 440 berbasis 22ilin Xilinx, seorang insinyur dapat mensimulasikan 10 core Arm Cortex A9 bersamaan. Dengan UltraScale + VU19P baru, insinyur yang sama dapat mensimulasikan 16 inti yang sama, karena peningkatan 1,6x gerbang logika. FPGA juga bertindak sebagai dasar untuk desain dan teknologi terbaru, dengan logika IO spesifik yang dapat dibangun ke dalam teknologi komunikasi saat ini dan masa depan. Gagasan tentang FPGA membuatnya lebih dapat dikonfigurasi daripada CPU, tetapi konfigurasi itu kemudian dapat dibawa ke perangkat hebat dan dibuat menjadi chip yang dioptimalkan untuk kinerja dan kepadatan yang lebih baik. Pada akhirnya untuk merancang CPU, Anda membutuhkan FPGA.

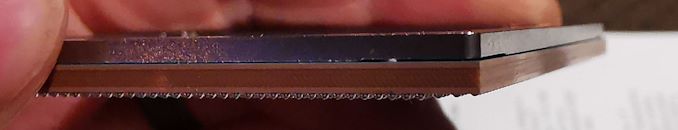

Dalam pengumuman itu, Xilinx menjelaskan bahwa bagian yang cukup besar dari bisnisnya adalah melayani pasar simulasi dan persaingan ini, yang digunakan oleh semua vendor chip, dan dorongan untuk chip yang lebih besar memberi mereka dorongan untuk membuat VU19P. Dibangun di atas proses 16FF + TSMC dengan teknologi CoWoS, VU19P sebenarnya dibangun sebagai empat segmen kemudian ditempatkan pada cetakan, namun chip tersebut bertindak sebagai satu bagian besar silikon yang tak terlihat, berjumlah 35 miliar transistor. Seiring dengan gerbang logika 9m, ada juga lebih dari 2000 segmen IO untuk bandwidth transceiver 4,5 Terabit (80 lajur 28G) dan bandwidth memori DDR4 1,5 Terabit, yang menurut perusahaan akan membantu pelanggannya membuat desain yang menampilkan banyak chip VU19P dalam satu sistem dengan topologi konektivitas all-to-all.

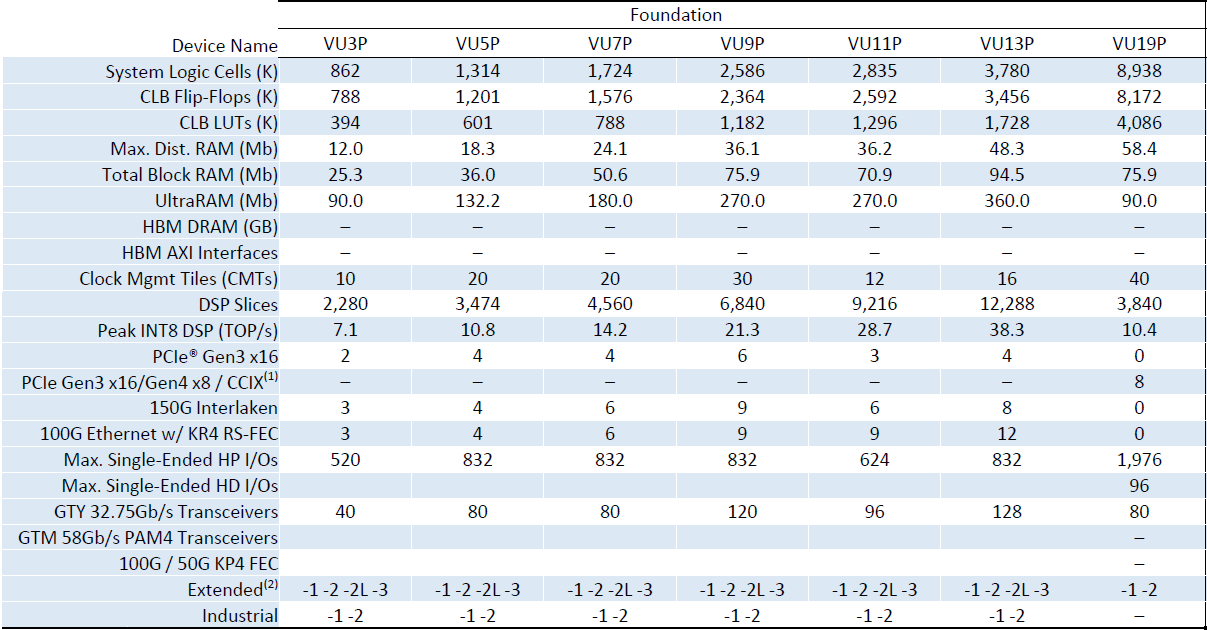

Dalam bentuk kartu PCIe, VU19P dapat dibangun sebagai perangkat PCIe 3.0 x16 atau PCIe 4.0 x8, atau sebagai chip terpisah dapat digunakan dalam paket 65×65 dengan koneksi BGA3825 dengan potensi konektivitas CCIX. Fitur perangkat keras lainnya termasuk Flip-Flops 8.2m CLB, LUT CLB 4.1m, UltraRAM 90 Mb, 40 Clock Management Tiles (CMTs), dan 3840 irisan DSP. Beberapa dari angka-angka itu sedikit lebih kecil dari UltraScale + VU13P, yang hanya memiliki gerbang logika 4m, tetapi ini disebabkan oleh keseimbangan sumber daya yang dinyatakan Xilinx akan mendukung pasar simulasi dan persaingan.

Seiring dengan VU19P, perusahaan juga akan membuat peningkatan pada perangkat lunak Vivado Design Suite untuk membantu dengan co-optimalisasi chip baru. Xilinx diatur untuk membawa VU19P ke pasar pada musim gugur 2020 (~ Q3), dan akan siap untuk memulai pengambilan sampel mitra utama pada paruh pertama 2020.

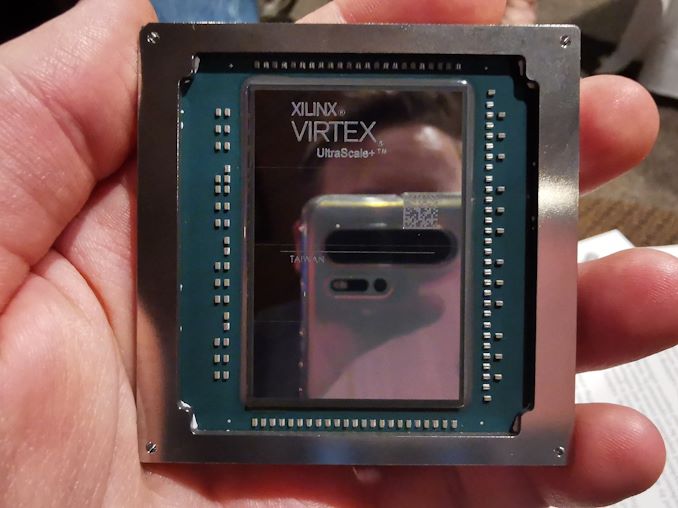

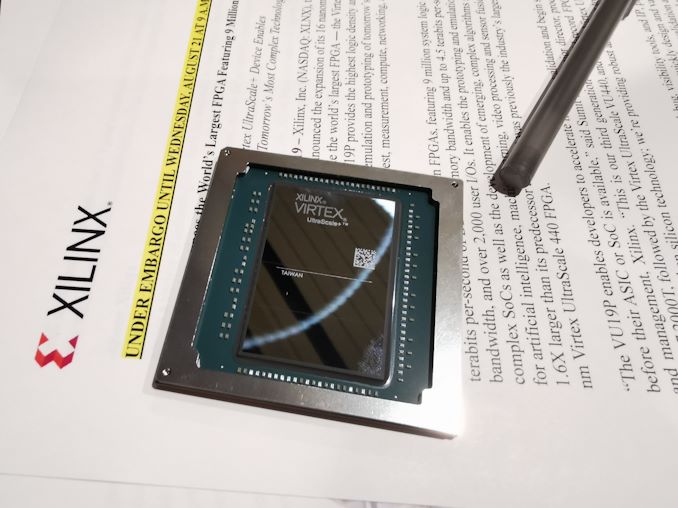

Saya menemukan sebuah chip. Nya @XilinxInc'FPGA terbesar baru' yang pernah ada, Virtex Ultrascale + VU19P dengan lebih dari 9 juta sel logika, 35 miliar transistor, dan 80 x 28G IO. Dibangun pada TSMC 16FF +, hadir pada Q3 2020. pic.twitter.com/mn30mtenMY

– Dr. Ian Cutress (@IanCutress) 21 Agustus 2019

Bacaan terkait: